# Static Random Access Memories (sRAM) Instructor - Bruce Bateman, Cypress Semiconductor

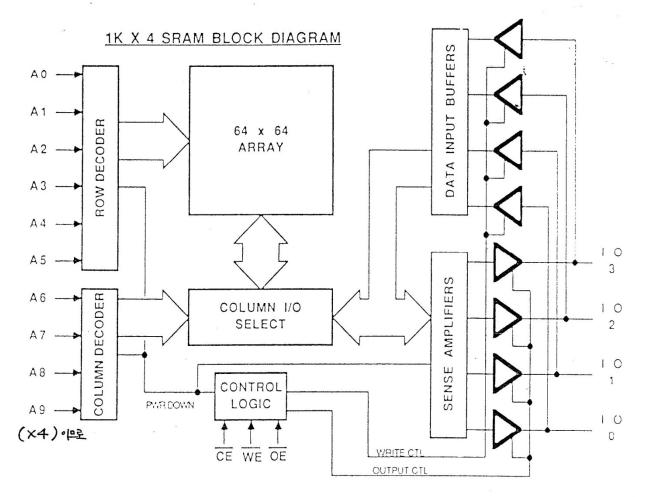

- Basic Architecture

- Storage Cell

- Address Decoding

- Data Sensing

- READ/WRITE Control

SRAM.

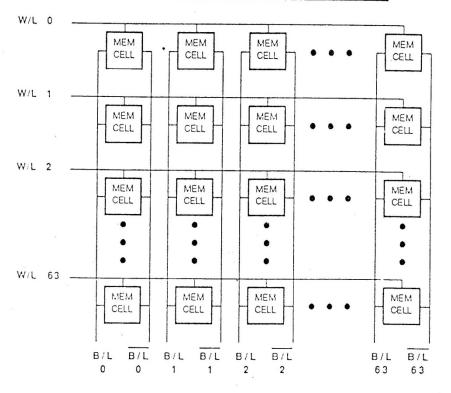

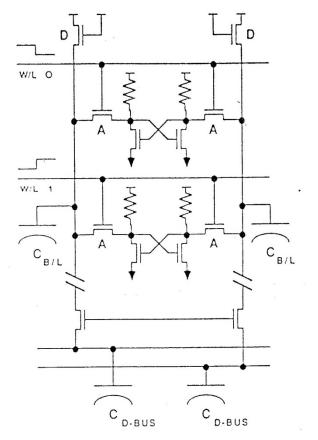

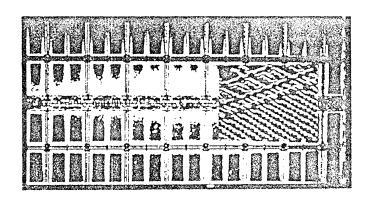

#### 4K SRAM MEMORY ARRAY

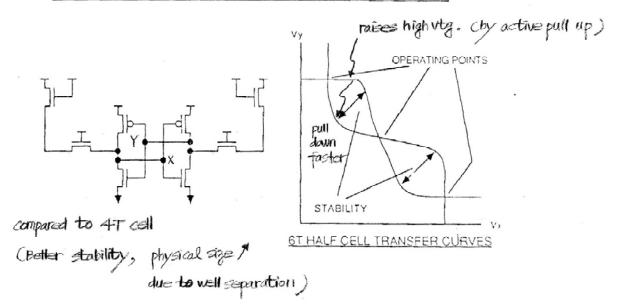

#### 6T MEMORY CELL "READ" STABILITY

#### MEMORY CELL ASYMETRY

#### CAUSES:

- . DESIGN MISMATCH DIFFERENT LAYOUT/SIZE

- PROCESS MISMATCH VI, CDs. ETC

ALIGNMENT SENSITIVITY WIDTH, LENGTH

Forting dimension

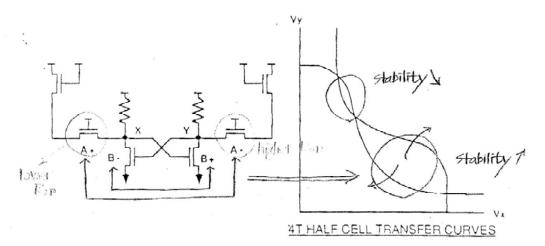

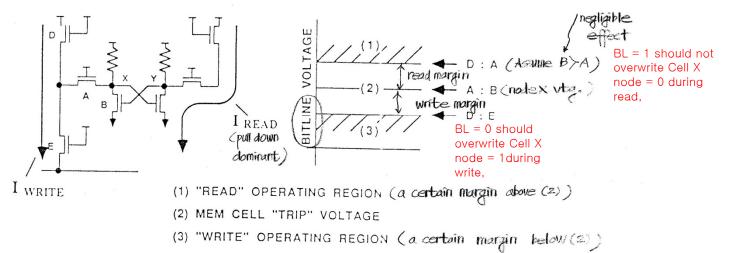

#### 4T MEMORY CELL READ/WRITE OPERATION

## Imagine voltage divider

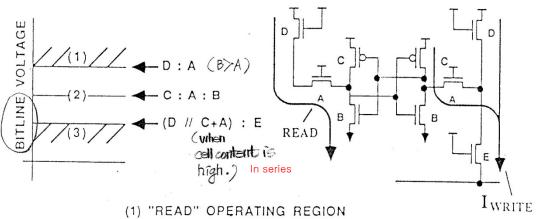

#### MEMORY CELL READ/WRITE OPERATION

- (1) "READ" OPERATING REGION

- (2) MEM CELL "TRIP" VOLTAGE

- (3) "WRITE" OPERATING REGION

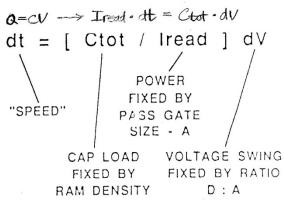

#### MEMORY CELL SPEED VR. POWER

During read, B effect is negligible since it is large

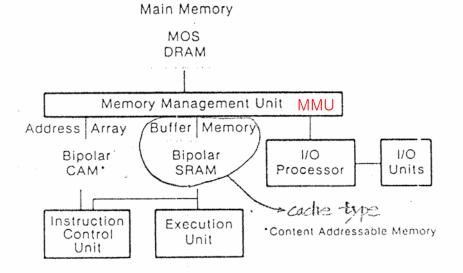

#### DRAM - Dynamic Random-Access Memory

1988 IEDM Short Course on Microprocessor and Memories

Nicky C.-C. Lu

Research Division

Thomas J. Watson Research Center, Yorktown Heights, NY 10598

### 1. DRAM And Its Development

- 1.1 Background And Definition

- 1.2 DRAMs in Systems: Examples

- 1.3 Product Environments And Trends

#### DRAM Chip

- Cell Arrays And Peripheral Circuits

- Array Utilization = (Cell Area × Total Bits)/(Chip Area)

- Key: Small Cell Area,

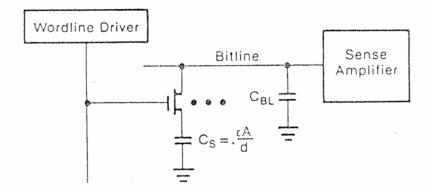

#### One-Transistor Cell

- An Access Transistor Plus A Storage Capacitor

- Selected By Wordline

- Signal Developed on Bitline

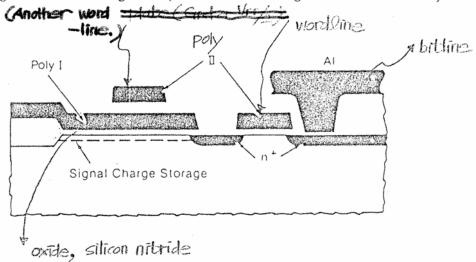

#### Planar Cell Structure

- Planar Transistor Plus Planar Capacitor in Silicon

- Uses Two Polysilicon Layers

- Storage-Node Leakage Requires Refreshing Data Periodically

#### **DRAM** Definition

- Randomly Addressable Memory (Versus Serial Memory)

- Electrically Read and Write Data at Will in Any Sequence

- Needs Refresh Periodically

- Volatile (Unless By Battery Backup)

#### DRAM in Mainframe

- Today: ≃1GB (8,000 1Mb DRAM Chips)

- By 1995: ≥64GB (Needs 8,000 64Mb DRAM Chips)

(Figure from Ref. B-6)

Nicky Lu 8/88

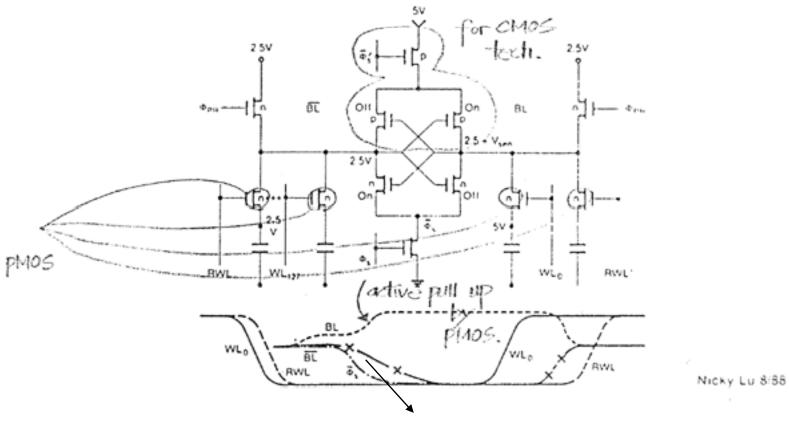

### 2. Chip/Circuit Design

- 2.1 Basic DRAM Operations

- 2.2 Design Example: A 512Kb CMOS High Speed DRAM

- 2.3 Notes on NMOS and BiCMOS DRAMs

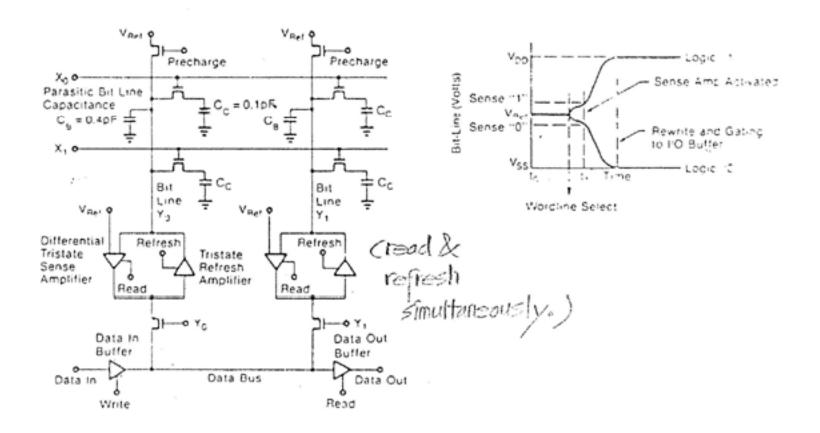

### Basic Array Design

(After Ref.)

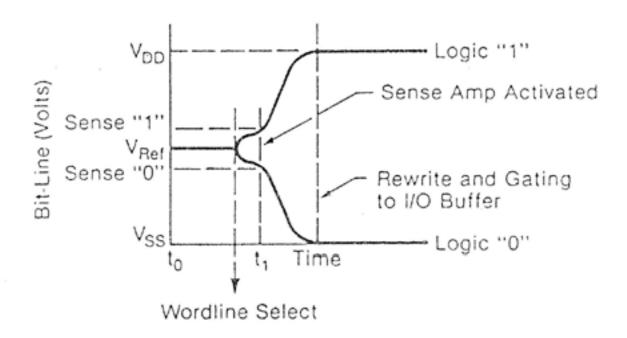

### Signal Development

#### Charge Transfer Ratio Concept (During Read)

• Storage Charge Capacity  $Q_s = C_sV_s = 2(C_s + C_B)V_{sen}$

### Cell Design Basics

•

$$V_{sen} + \Delta V = \frac{1}{2(C_S + C_B)} \cdot \frac{\epsilon_A V_S}{d}$$

Where AV: Noise

ε: Dielectric Constants

A: Storage Area

V<sub>S</sub>: Storage Signal

d: Dielectric Thickness

V<sub>s</sub>/d Limited By Maximum Dielectric Strength

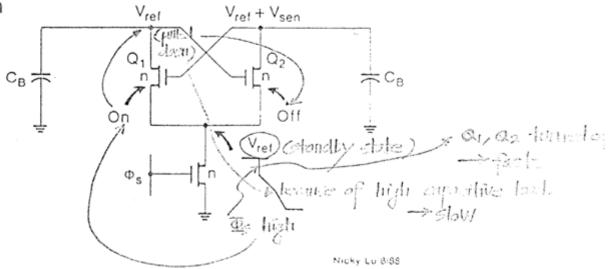

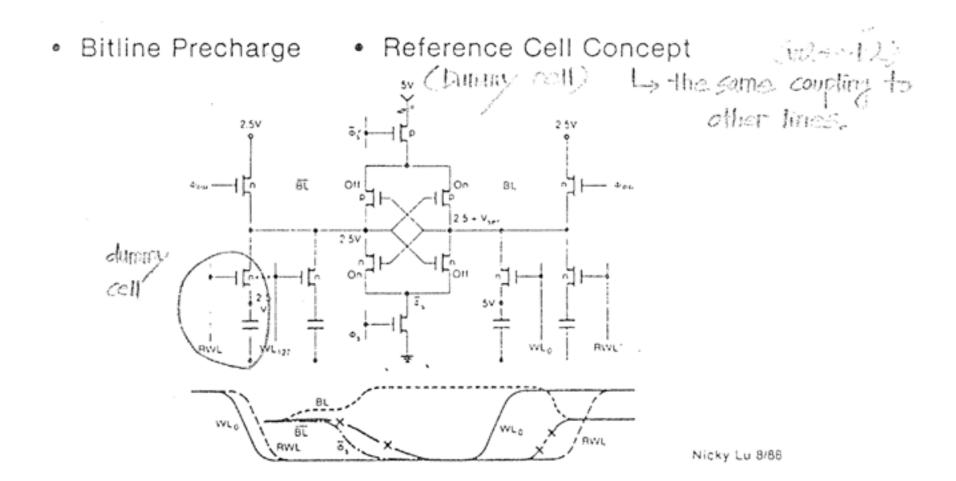

#### Cross-Coupled Sense Amplifier

- · Differential Signal Established

- Latching

- Amplification

### Sensing Circuits

CMOS Cross-Coupled Latch

Phi pulled down then bit line change

### Sensing Circuits

### Sensing Circuits

• Self Restore • Refresh

Solf Restore • Refresh

The state of the sta

Nicks Lu 5 55