## TFT-LCD Overview

## 1. TFT - LCD 구동 및 구조

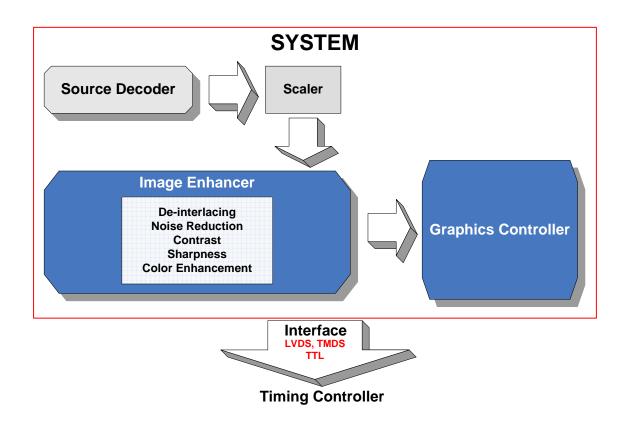

TFT-LCD 의 구동은 압축된 Image Data 를 받아 Decoding 하고 화질 개선을 위한 여러 가지 process 를 거친 후 panel 에 display 가능한 format 으로 내보내는 System 부분과 이렇게 받은 data 를 실제 display 하는 panel 부분으로 나누어져 있다.

< Fig. 1 TFT-LCD panel - System 부분 >

우선 Source Decoder 는 mpeg 등의 형식으로 압축되어 있는 Data 를 받아 Decoding 한 후 Scaler 로 넘어가게 된다. Scaler 는 해상도 변환을 통해 원하는 해상도의 Data 를 출력하게 된다. Image Enhancer 는 Display 고급화의 핵심이 되는 부분으로 Interlacing 기법과 Progressive scan 방법을 혼합한 De-Interlacing, Noise Reduction, Contrast 보정, Sharpness 보정, Color Enhancement 등을 행하는 DSP core 가 이에 해당된다. 이렇게 Enhancement 과정을 거진 Data 는 Panel 로 넘어가기 위한 최종 관문인 Graphics Controller 로 입력된다. Graphics Controller 는 받은 Pixel 의 Data 를 R, G, B 로 자르고 LCD Panel 의 Display Timing 을 위한 Syncing Signal 등과 함께 Interface 를 통해 내보내게 된다.

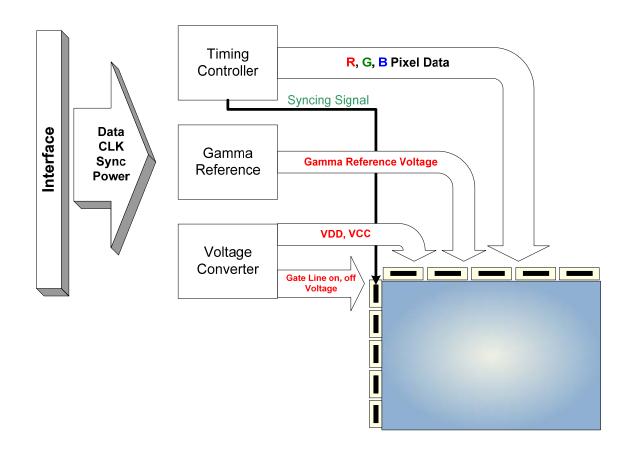

< Fig. 2 Panel 구동의 중요 Part 와 구동 원리 >

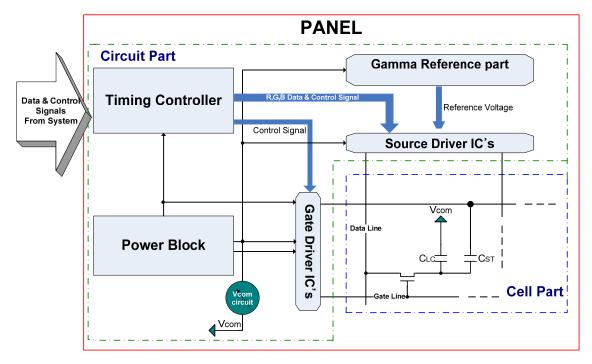

< Fig. 3 TFT-LCD - Panel 세부 구조 >

System 과 Panel 은 Interface 로 연결되어 있다. System 에서 보내지는 pixel 및 control data 는 LVDS, TMDS signal 을 이용하는 경우 Receiver 가 Interface 역할을 하여 Timing Controller 로 해당 data를 보내게 된다. Timing Controller 는 Source, Gate Driver IC 가 사용할 수 있는 형태로 Display Data 와 Control Signal 들을 변환하여 내보낸다. Gamma reference part 에서는 Source Driver IC 의 reference 전압을 조절한다. Source Driver IC 는 Display Data 를 Analog 전압으로 변환하여 Cell 로 공급하며 Gate Driver IC 는 Control Signal 에 따라 Analog 전압 필스파형을 Cell 로 공급한다. Cell 의 원활한 Display 를 위해 높은 전압이 필요한데 이것을 Vcom circuit 에서 생성하여 Source Driver 를 통해 공급하게 된다. 이러한 모든 내부 Block 들의 구동전원은 Power Block 에서 생성하여 공급된다.

## 2. TFT - LCD: Panel 구동 및 Display

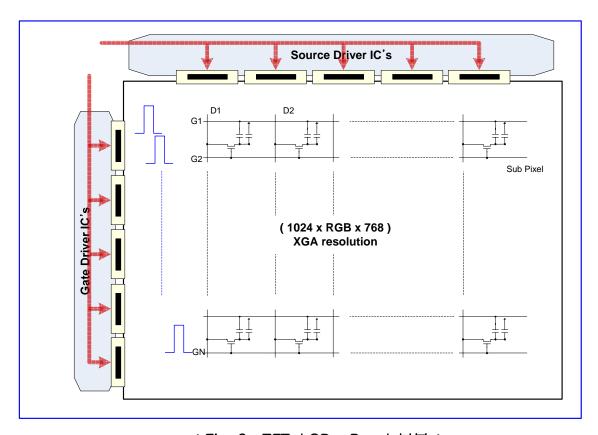

Color TFT - LCD Panel 구동

< Fig. 8 TFT-LCD - Panel 부분 >

< Fig. 9 Cell Ass'y Display >

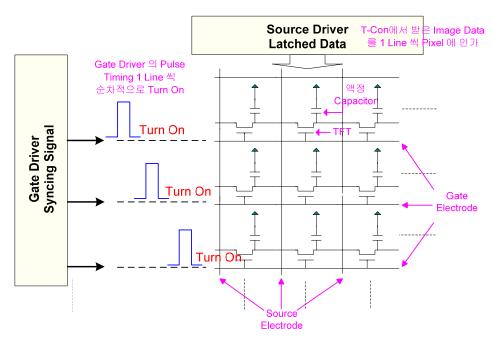

Source Driver IC 는 Timing Controller 에서 1Line 의 RGB Data 를 받은 후 Latch 한다. Timing Controller 는 Vsync 와 Hsync Signal 을 받아 Gate Driver IC 에 전달하고 Gate Driver 에서는 Horizontal 1 Line 의 TFT 를 ON 시키는 Control Signal 을 Gate Line 에 인가한다. Pixel 의 Data 들은 Source Driver 에서 Analog 전압으로 변환되어 Data Line 에 인가되는데 이 때 Gate Driver 에 의해 ON 된 Line 에서 Display 가 가능해진다.

Color TFT LCD - Gate Driver

< Fig. 10 Gate Driver 구조 및 동작 >

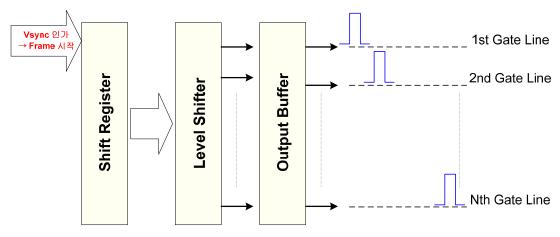

위 그림은 Gate Driver 의 구조 및 동작을 나타내고 있다. Timing Controller 에서 Frame 의 시작을 알리는 Vsync Signal 을 보내면 이 신호를 받아 Shift Register 가 순차적으로 펄스를 인가한다. 이 펄스는 Level Shifter 를 통과하여 TFT 를 ON 시킬 수 있는 Threshold Voltage 이상으로 증폭되고 다시 Buffer 를 통과하여 Gate Line 에 인가된다.

Level Shifter 는 아래와 같이 Input Level Shifter 와 Level Shifter 로 나뉘어져 Line 에 인가되는 Threshold Voltage 이상의 높은 전압을 발생시키게 된다.